### **General Description**

The IETF PWE3 SAToP/CESoPSN/HDLC-compliant DS34S132 provides the interworking functions that are required for translating TDM data streams into and out of TDM-over-Packet (TDMoP) data streams for L2TPv3/IP, UDP/IP, MPLS (MFA-8), and Metro Ethernet (MEF-8) networks while meeting the jitter and wander timing performance that is required by the public network (ITU G.823, G.824, and G.8261). Up to 32 TDM ports can be translated into as many as 256 individually configurable pseudowires (PWs) for transmission over a 100/1000Mbps Ethernet port. Each TDM port's bit rate can vary from 64Kbps to 2.048Mbps to support T1/E1 or slower TDM rates. PW interworking for TDM-based serial HDLC data is also supported. A built-in time-slot assignment (TSA) circuit provides the ability to combine any group of time slots (TS) from a single TDM port into a single PW. The high level of integration provides the perfect solution for high-density applications to minimize cost, board space, and time to market.

# **Applications**

TDM Circuit Emulation Over PSN

TDM Leased-Line Services Over PSN

TDM Over BPON/GPON/EPON

TDM Over Cable

TDM Over Wireless

Cellular Backhaul

Multiservice Over Unified PSN

HDLC-Encapsulated Data Over PSN

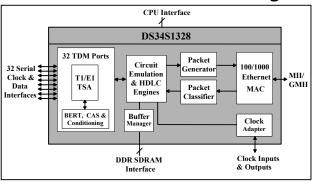

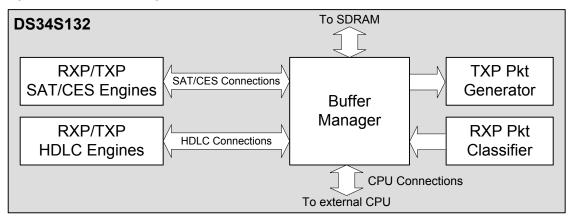

### Functional Diagram

#### Features

- ◆ 32 Independent TDM Ports with Serial Data, Clock, and Sync (Data = 64Kbps to 2.048Mbps)

- ♦ One 100/1000Mbps (MII/GMII) Ethernet MAC

- ♦ 256 Total PWs, 32 PW per TDM Port, with Any Combination of TDMoP and/or HDLC PWs

- PSN Protocols: L2TPv3 or UDP Over IP (IPv4 or IPv6), Metro Ethernet (MEF-8), or MPLS (MFA-8)

- ♦ 0, 1, or 2 VLAN Tags (IEEE 802.1Q)

- Synchronous or Asynchronous TDM Port Timing

One Clock Recovery Engine per TDM Port with One Assignable as a Global Reference Supported Clock Recovery Techniques Adaptive Clock Recovery Differential Clock Recovery Absolute and Differential Timestamps Independent Receive and Transmit Interfaces Two Clock Inputs for Direct Transmit Timing

- ♦ For Structured T1/E1, Each TDM Port Includes DS0 TSA Block for any Time Slot to Any PW 32 HDLC/CES Engines (256 Total) With or Without CAS Signaling

- For Unstructured, each TDM Port Includes One HDLC/SAT Engine (32 Total)

Any data rate from 64Kbps to 2.048Mbps

- ♦ 32-Bit or 16-Bit CPU Processor Bus

- ♦ CPU-Based OAM and Signaling

UDP-specific "Special" Ethernet Type

Inband VCCV ARP

MEF OAM NDP/IPv6

**Broadcast DA**

- **♦ DDR SDRAM Interface**

- ♦ Low-Power 1.8V Core, 3.3V I/O, 2.5V SDRAM

# **Ordering Information**

| PART          | PORTS | TEMP RANGE     | PIN-PACKAGE |

|---------------|-------|----------------|-------------|

| DS34S132GNA2  | 32    | -40°C to +85°C | 676 BGA     |

| DS34S132GNA2+ | 32    | -40°C to +85°C | 676 BGA     |

+Denotes a lead(Pb)-free/RoHS-compliant package.

MIXIM

Maxim Integrated Products 1

Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: <a href="https://www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>. For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **TABLE OF CONTENTS**

| 1 | Introduction                                                                        |    |

|---|-------------------------------------------------------------------------------------|----|

| 2 | Acronyms and Glossary                                                               |    |

| 3 | Applicable Standards                                                                |    |

| 4 | High Level Description                                                              |    |

| 5 | Application Examples                                                                |    |

| 6 | Block Diagram                                                                       |    |

| 7 | Features                                                                            |    |

| 8 | Pin Descriptions                                                                    |    |

|   | 8.1 Short Pin Descriptions                                                          |    |

| _ | 8.2 Detailed Pin Descriptions                                                       |    |

| 9 | Functional Description                                                              |    |

|   | 9.1 Connection Types                                                                |    |

|   | 9.1.1 SAT/CES Payload Connections                                                   |    |

|   | 9.1.3 SAT/CES PW-Timing Connections                                                 |    |

|   | 9.1.4 CPU Connections                                                               |    |

|   | 9.2 TDM Port Functions                                                              |    |

|   | 9.2.1 TDM Port Related Input and Output Clocks                                      |    |

|   | 9.2.1.1 PW-Timing                                                                   | 33 |

|   | 9.2.1.1.1 RXP Clock Recovery (RXP PW-Timing)                                        |    |

|   | 9.2.1.1.2 TXP PW-Timing                                                             | 34 |

|   | 9.2.1.2 TDM Port - One Clock and Two Clock Modes                                    | 35 |

|   | 9.2.2 TDM Port Interface                                                            |    |

|   | 9.2.2.1 TDM Port Transmit Interface                                                 |    |

|   | 9.2.2.2 TDM Port Receive Interface                                                  |    |

|   | 9.2.3 TDM Port Structure & Frame Formats                                            |    |

|   | 9.2.4 Timeslot Assignment Block                                                     | 38 |

|   | 9.2.4.1 TDM CAS to Packet CAS Translation                                           | 40 |

|   | 9.2.4.2 TSA Block Loopbacks                                                         |    |

|   | 9.2.5 TDM Port Data Processing Engines                                              |    |

|   | 9.2.5.1 HDLC Engine                                                                 |    |

|   | 9.2.5.1.1 SAT/CES Engine                                                            |    |

|   | 9.2.5.2 TDM Port Priority                                                           |    |

|   | 9.2.5.3 Jitter Buffer Settings                                                      |    |

|   | 9.2.6 TDM Diagnostic Functions                                                      |    |

|   | 9.2.6.1 TDM Loopback                                                                |    |

|   | 9.2.6.2 TDM BERT                                                                    |    |

|   | 9.3 Packet Processing Functions                                                     |    |

|   | 9.3.1 Ethernet MAC                                                                  |    |

|   | 9.3.1.1 Ethernet Port Diagnostic Functions                                          |    |

|   | 9.3.1.1.2 Packet BERT                                                               |    |

|   | 9.3.2 RXP Packet Classification.                                                    |    |

|   | 9.3.2.1 Generalized Packet Classification                                           |    |

|   | 9.3.2.2 PW (BID and OAM BID) Packet Classification                                  |    |

|   | 9.3.2.2.1 UDP Settings                                                              |    |

|   | 9.3.2.2.2 Handling of Packets with a Matching BID or OAM BID                        | 58 |

|   | 9.3.2.2.3 L-bit Signaling for RXP PWs                                               |    |

|   | 9.3.2.3 CPU Packet Classification                                                   | 59 |

|   | 9.3.2.3.1 Packets with Broadcast Ethernet DA (DPC.CR1.DPBTP and DPC.CR1.DPBCP)      | 60 |

|   | 9.3.2.3.2 Packets with Unknown Ethernet DA (PC.CR7 – PC.CR19 and DPC.CR1.DPS9)      |    |

|   | 9.3.2.3.3 PW Packets with Unknown PW-ID (DPS6)                                      | 60 |

|   | 9.3.2.3.4 MEF OAM Ethernet Type Packets (MOET)                                      | 60 |

|   | 9.3.2.3.5 CPU Destination Ethernet Type Packets (CDET and DPS8)                     | 60 |

|   | 9.3.2.3.6 ARP Packet with Known IP Destination Address (PC.CR6 – PC.CR8 and DPS3)   | 60 |

|   | 9.3.2.3.7 ARP Packet with Unknown IP Destination Address (PC.CR6 – PC.CR8 and DPS0) |    |

|   | 9.3.2.3.8 Packet with Unknown Ethernet Type (DPS2)                                  | 60 |

| 9.3.2.3.9 IP Packets with Unknown IP Protocol (DPS4)                                 | 60   |

|--------------------------------------------------------------------------------------|------|

| 9.3.2.3.10 IP Packet with Unknown IP Destination Address (PC.CR6 – PC.CR16 and DPS1) | 60   |

| 9.3.2.3.11 "CPU Debug RXP PW Bundle" Setting (RXBDS)                                 | 61   |

| 9.3.2.3.12 PW Bundle with Unknown UDP Protocol Type (UPVCE and DPS5)                 | 61   |

| 9.3.2.3.13 PW Bundle In-band VCCV OAM (RXOICWE and DPS7)                             |      |

| 9.3.2.3.14 PW Bundle with Too Many MPLS Labels (DPS10)                               |      |

| 9.3.2.3.15 PW OAM Bundle - Out-band VCCV OAM Packets (DPS7)                          |      |

| 9.3.3 TXP Packet Generation                                                          |      |

| 9.3.3.1 TXP SAT/CES/HDLC/Clock Only PW Packet Generation                             |      |

| 9.3.3.1.1 L-bit Signaling                                                            |      |

| 9.3.3.2 TXP CPU Packet Generation                                                    | 63   |

| 9.3.3.3 TXP Packet Scheduling                                                        |      |

| 9.3.3.4 TXP Packet Queue Monitoring                                                  |      |

| 9.4 CPU Packet Interface                                                             |      |

| 9.4.1 RXP CPU Packet Interface                                                       |      |

|                                                                                      |      |

| 9.4.2 TXP CPU Packet Interface                                                       |      |

| 9.5 Clock Recovery Functions                                                         |      |

| 9.6 Miscellaneous Global Functions                                                   |      |

| 9.6.1 Global Resets                                                                  |      |

| 9.6.2 Latched Status and Counter Register Reset                                      |      |

| 9.6.3 Buffer Manager                                                                 |      |

| 9.6.3.1 SDRAM Interface                                                              |      |

| 9.6.4 CPU Electrical Interconnect                                                    |      |

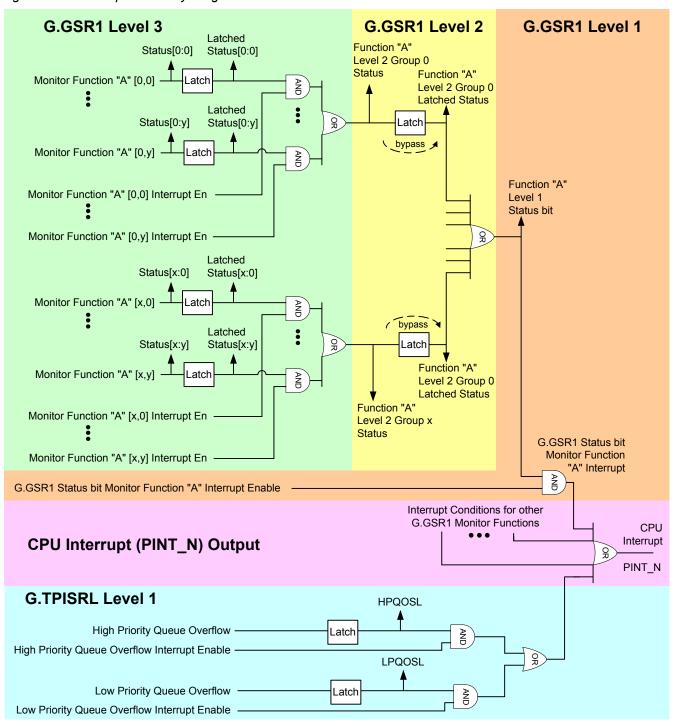

| 9.6.5 Interrupt Hierarchy                                                            |      |

| 0 Device Registers                                                                   | 74   |

| 10.1 Register Block Address Ranges                                                   | 74   |

| 10.2 Register Address Reference List                                                 | 75   |

| 10.3 Register Definitions                                                            | 83   |

| 10.3.1 Global Registers (G.)                                                         | 83   |

| 10.3.1.1 Global Configuration Registers (G.)                                         |      |

| 10.3.1.2 Global Status Registers (G.)                                                |      |

| 10.3.1.3 Global Status Register Interrupt Enables (G.)                               |      |

| 10.3.2 Bundle Registers (B.)                                                         |      |

| 10.3.2.1 Bundle Reset Registers (B.)                                                 |      |

| 10.3.2.2 Bundle Data Control Registers (B.)                                          |      |

| 10.3.2.3 Bundle Data Registers (B.)                                                  |      |

| 10.3.2.4 Bundle Status Latch Registers (B.)                                          |      |

| 10.3.2.5 Bundle Status Register Interrupt Enables (B.)                               |      |

| 10.3.3 Jitter Buffer Registers (JB.)                                                 |      |

| 10.3.3.1 Jitter Buffer Status Registers (JB.)                                        |      |

| 10.3.3.2 Jitter Buffer Status Register Interrupt Enables (JB.)                       |      |

| 10.3.3.2 Julier Durier Status Register Interrupt Enables (JD.)                       | 1107 |

| 10.3.4 Packet Classifier Registers (PC.)                                             | 110  |

|                                                                                      |      |

| 10.3.4.2 Packet Classifier Status Register Latches (PC.)                             |      |

| 10.3.4.3 Packet Classifier Status Register Interrupt Enables (PC.)                   |      |

| 10.3.4.4 Packet Classifier Counter Registers (PC.)                                   |      |

| 10.3.5 External Memory Interface Registers (EMI.)                                    | 115  |

| 10.3.5.1 External Memory Interface Configuration Registers (EMI.)                    |      |

| 10.3.5.2 External Memory Interface Status Registers (EMI.)                           |      |

| 10.3.5.3 External Memory Interface Status Register Interrupt Enables (EMI.)          |      |

| 10.3.5.4 External Memory DLL/PLL Test Registers (EMI.)                               |      |

| 10.3.6 External Memory Access Registers (EMA.)                                       |      |

| 10.3.6.1 Write Registers (EMA.)                                                      |      |

| 10.3.6.2 Read Registers (EMA.)                                                       |      |

| 10.3.7 Encap BERT Registers (EB.)                                                    |      |

| 10.3.8 Decap BERT Registers (DB.)                                                    |      |

| 10.3.9 Miscellaneous Diagnostic Registers (MD.)                                      | 126  |

| 10.3.10 Test Registers (TST.)                                                        | 127  |

| 10.3.11 Clock Recovery Registers (CR.)                                               | 129  |

|                                                                                      |      |

| 10.3.12 MAC Registers (M.)                                                      | 120 |

|---------------------------------------------------------------------------------|-----|

| 10.3.13 TXP SW CAS Registers (TXSCn.)                                           |     |

| 10.3.14 Xmt (RXP) SW CAS Registers (RXSCn.)                                     |     |

| 10.3.15 TDM Port n Registers (Pn.; n = 0 to 31)                                 |     |

| 10.3.15.1 Port n Transmit Configuration Registers (Pn.)                         | 140 |

| 10.3.15.2 Port n Transmit Status Registers (Pn.)                                | 142 |

| 10.3.15.3 Port n Transmit Status Register Latches (Pn.)                         |     |

| 10.3.15.4 Port n Transmit Status Register Interrupt Enables (Pn.)               | 143 |

| 10.3.15.5 Port n Receive Configuration Registers (Pn.)                          | 144 |

| 10.3.15.6 Port n Receive Status Registers (Pn.)                                 |     |

| 10.3.15.7 Port n Receive Status Register Latches (Pn.)                          |     |

| 10.3.15.8 Port n Receive Status Register Interrupt Enables (Pn.)                |     |

| 10.3.16 Timeslot Assignment Registers (TSAn.m.; "n" = TDM Port n; "m" = Timeslo |     |

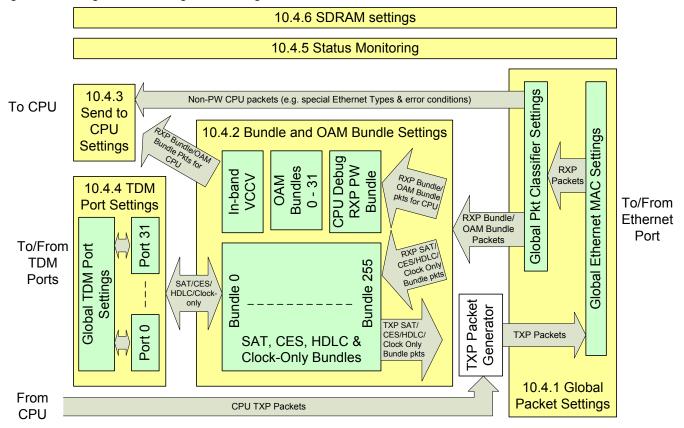

| 10.4 Register Guide                                                             |     |

| 10.4.1 Global Packet Settings                                                   |     |

| 10.4.2 Bundle and OAM Bundle Settings                                           |     |

| 10.4.2.1 SAT Bundle Settings                                                    |     |

| 10.4.2.2 CES without CAS Bundle Settings                                        | 153 |

| 10.4.2.3 CES with CAS Bundle Settings                                           | 154 |

| 10.4.2.4 Unstructured HDLC Bundle (any Line Rate) Settings                      | 155 |

| 10.4.2.5 Structured Nx64 Kb/s HDLC Bundle Settings                              | 156 |

| 10.4.2.6 Structured 16 Kb/s or 56 Kb/s HDLC Bundle Settings                     | 157 |

| 10.4.2.7 Clock Only Bundle Settings                                             | 158 |

| 10.4.2.7.1 Combined RXP and TXP (Bidirectional) Clock Only Bundle Settir        |     |

| 10.4.2.7.2 RXP (Unidirectional) Clock Only Bundle Settings                      |     |

| 10.4.2.7.3 TXP (Unidirectional) Clock Only Bundle Settings                      |     |

| 10.4.2.8 "CPU RXP PW Debug" Bundle Settings                                     |     |

| 10.4.2.9 In-band VCCV OAM Connection Settings                                   | 162 |

| 10.4.2.10 OAM Bundle (Out-band VCCV OAM) Settings                               |     |

| 10.4.3 Send to CPU Settings                                                     | 163 |

| 10.4.4 TDM Port Settings                                                        |     |

| 10.4.5 Status Monitoring                                                        | 167 |

| 10.4.5.1 Ethernet Port Monitoring                                               | 167 |

| 10.4.5.2 Global Packet Classifier Monitoring Control                            | 168 |

| 10.4.5.3 Global RXP Bundle Monitoring Control                                   | 168 |

| 10.4.5.4 Global TXP Packet Queue Monitoring                                     |     |

| 10.4.5.5 PW Bundle Monitoring                                                   |     |

| 10.4.6 SDRAM Settings                                                           | 169 |

| 11 JTAG Information                                                             |     |

| 12 DC Electrical Characteristics                                                |     |

| 13 AC Timing Characteristics                                                    |     |

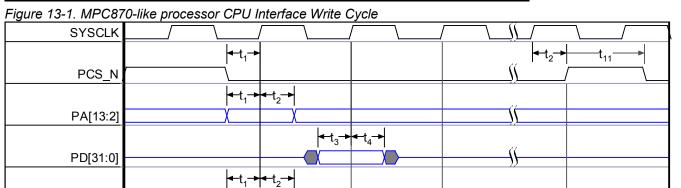

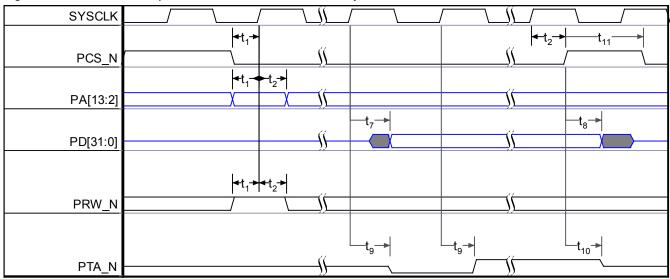

| 13.1 CPU Interface                                                              |     |

| 13.2 TDM Interface                                                              |     |

| 13.3 MAC Interface                                                              |     |

| 13.3.1 GMII Interface                                                           |     |

| 13.3.2 MII Interface                                                            |     |

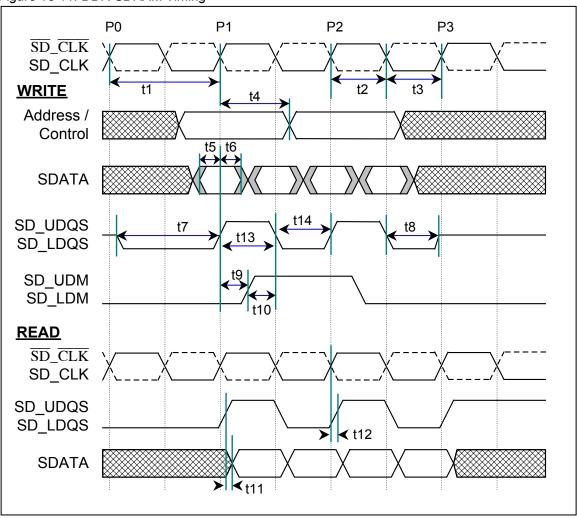

| 13.4 DDR SDRAM Timing                                                           |     |

| 14 Pin Assignment                                                               |     |

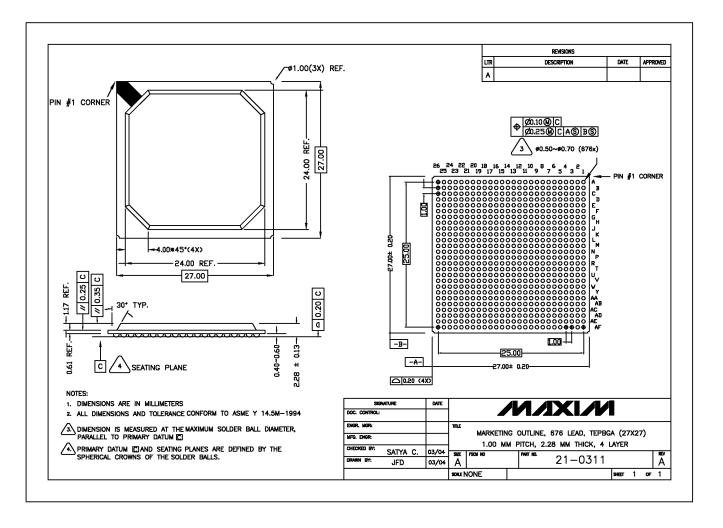

| 15 Package Information                                                          |     |

| 16 Thermal Information                                                          |     |

| 17 Data sheet Revision History                                                  | 194 |

# **LIST OF FIGURES**

| Figure 5-1. TDMoP in a Metropolitan Packet Switched Network                                       | 13  |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 5-2. TDMoP in Cellular Backhaul                                                            | 14  |

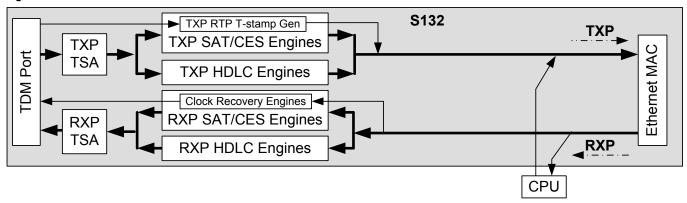

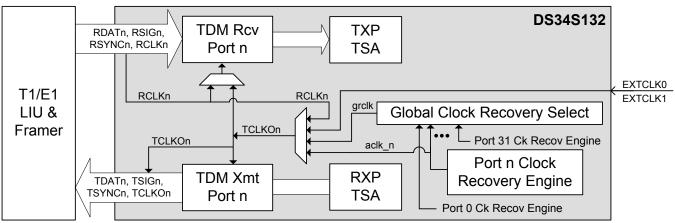

| Figure 6-1. DS34S132 Functional Block Diagram                                                     | 15  |

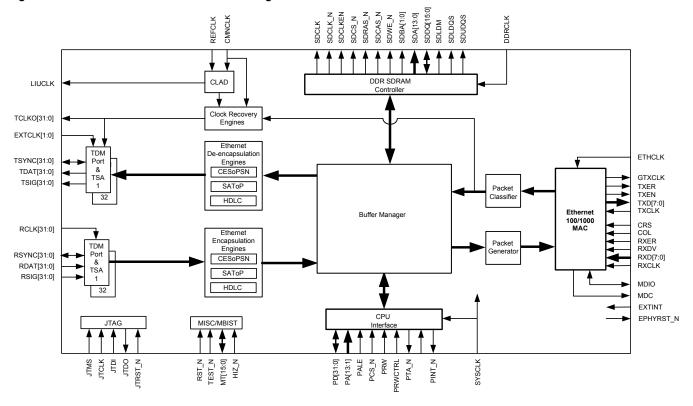

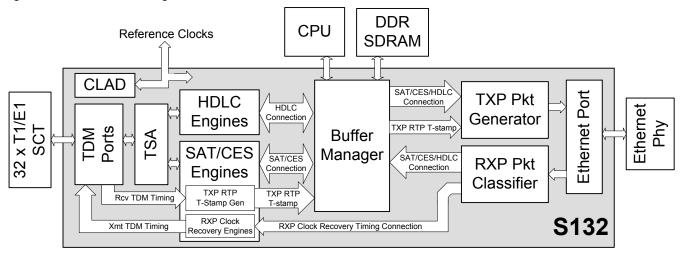

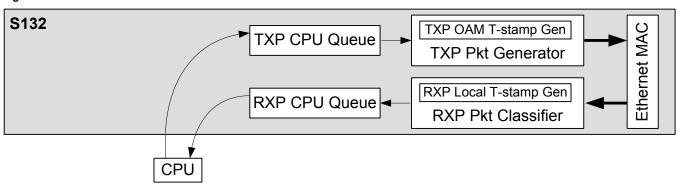

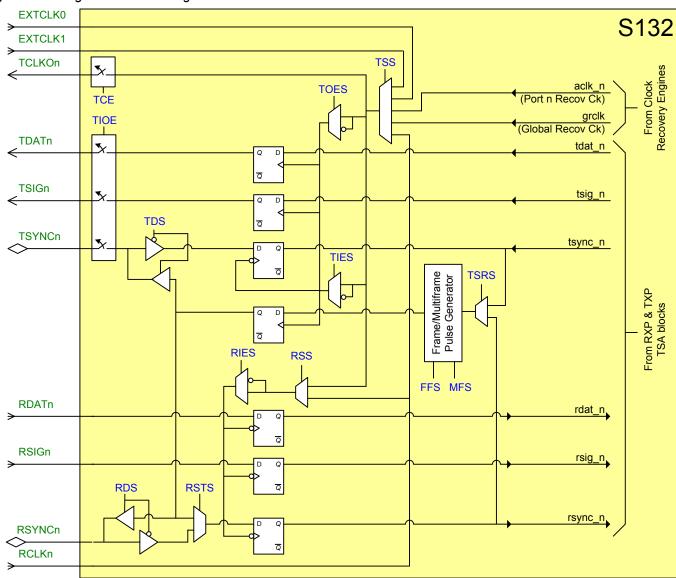

| Figure 9-1. S132 Block Diagram                                                                    | 28  |

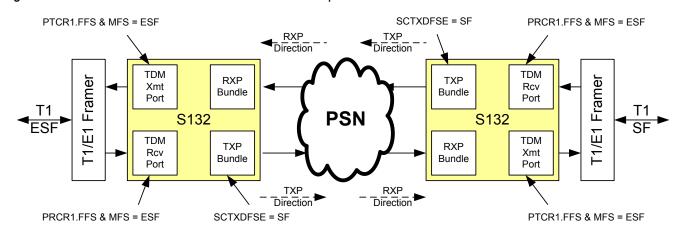

| Figure 9-2. RXP/TXP Data Path Directions                                                          | 28  |

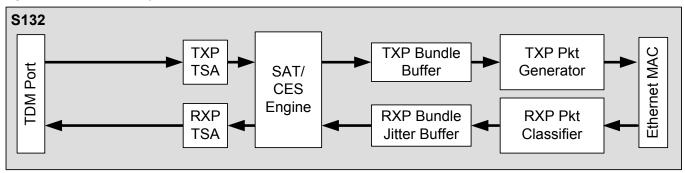

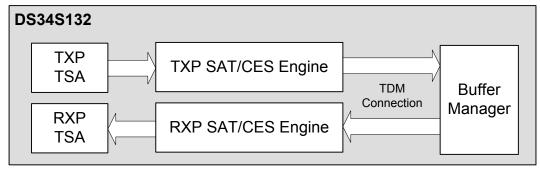

| Figure 9-3. SAT/CES Payload Connection                                                            |     |

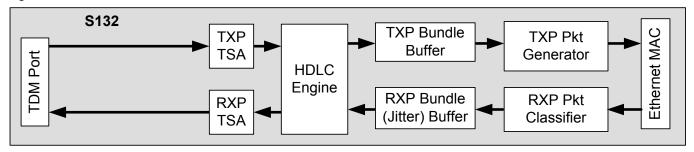

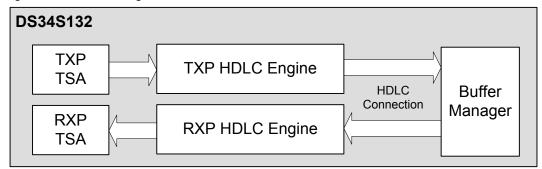

| Figure 9-4. Bundle HDLC Connection                                                                | 29  |

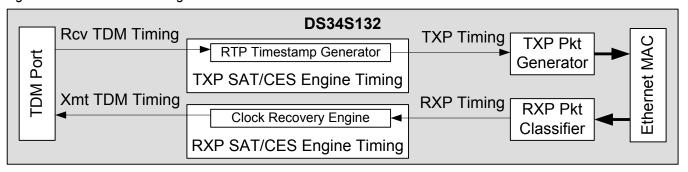

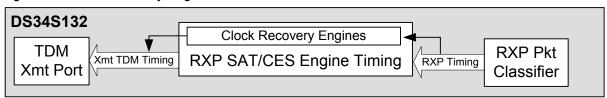

| Figure 9-5. Bundle PW-Timing Connections                                                          | 30  |

| Figure 9-6. CPU Connections                                                                       |     |

| Figure 9-7. TDM Port Input and Output Clock Overview                                              |     |

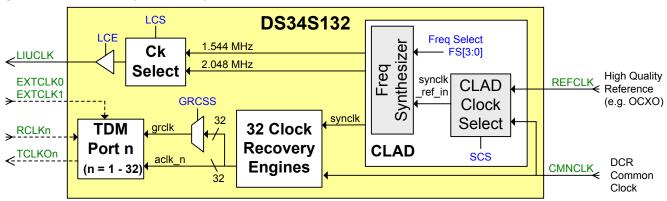

| Figure 9-8. Clock Recovery Engine Environment                                                     |     |

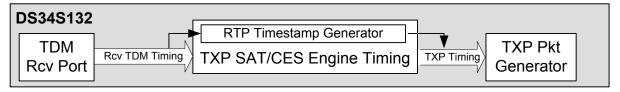

| Figure 9-9. TXP PW-Timing Environment                                                             |     |

| Figure 9-10. TDM Port #1 Environment                                                              |     |

| Figure 9-11. Logic Detail for a Single TDM Port Interface                                         |     |

| Figure 9-12. T1 ESF CAS to SF CAS Translation Example                                             |     |

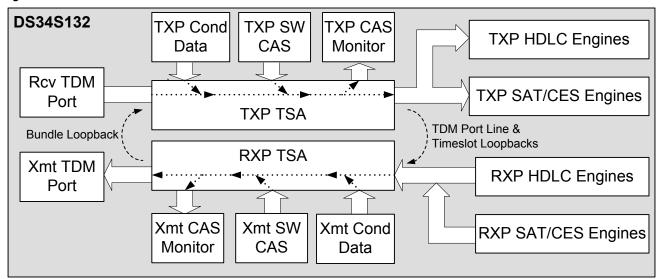

| Figure 9-13. TSA Block Environment                                                                | 39  |

| Figure 9-14. HDLC Engine Environment                                                              | 43  |

| Figure 9-15. SAT/CES Engine Environment                                                           | 44  |

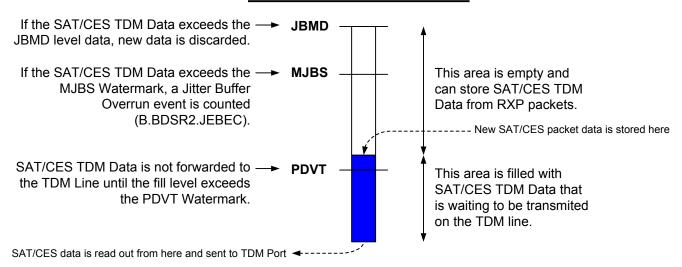

| Figure 9-16. Bundle Jitter Buffer FIFO                                                            |     |

| Figure 9-17. T1/E1 Port Line Loopback and TDM Port Timeslot Loopback Diagram                      |     |

| Figure 9-18. T1/E1 Port Bundle Loopback Diagram                                                   |     |

| Figure 9-19. TDM Port BERT Diagram                                                                |     |

| Figure 9-20. Ethernet MAC Environment                                                             |     |

| Figure 9-21. Ethernet Port Local Loopback                                                         |     |

| Figure 9-22. Ethernet Port BERT Diagram                                                           |     |

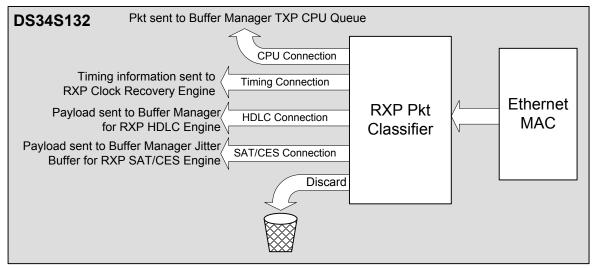

| Figure 9-23. RXP Packet Classifier Environment                                                    |     |

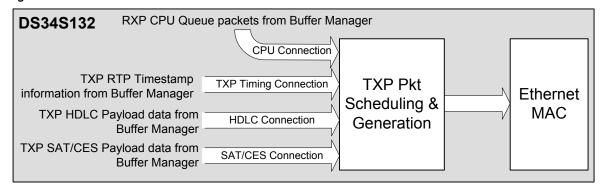

| Figure 9-24. TXP Packet Generation Environment                                                    |     |

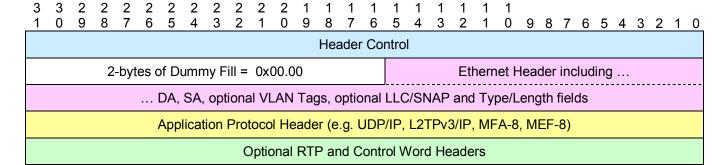

| Figure 9-25. SAT/CES/HDLC/Clock Only PW TXP Header Descriptor                                     |     |

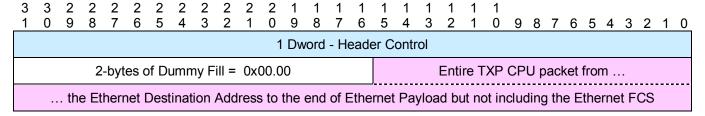

| Figure 9-26. Stored RXP CPU Packet                                                                |     |

| Figure 9-27. Stored TXP CPU Packet and Header Descriptor                                          |     |

| Figure 9-28. Buffer Manager Environment                                                           |     |

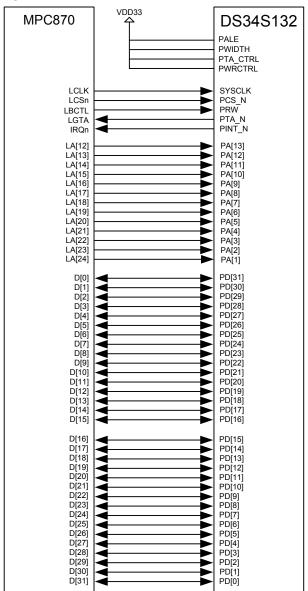

| Figure 9-29. MPC870 32-bit Bus Interface.                                                         |     |

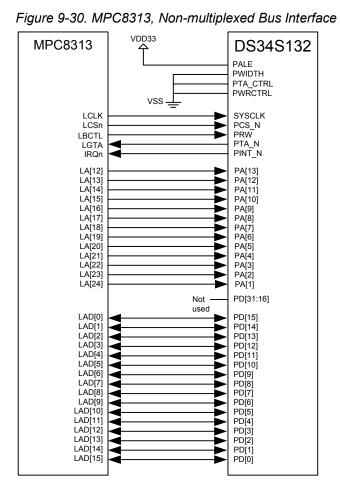

| Figure 9-30. MPC8313, Non-multiplexed Bus Interface                                               |     |

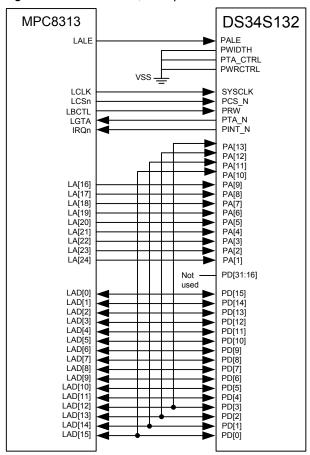

| Figure 9-31. MPC8313, Multiplexed Bus Interface                                                   | 71  |

| Figure 9-32. Interrupt Hierarchy Diagram                                                          |     |

| Figure 10-1. Register Guide High Level Diagram                                                    |     |

| Figure 13-1. MPC870-like processor CPU Interface Write Cycle                                      |     |

| Figure 13-2. MPC870-like processor CPU Interface Read Cycle                                       |     |

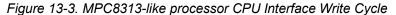

| Figure 13-3. MPC8313-like processor CPU Interface Write Cycle                                     |     |

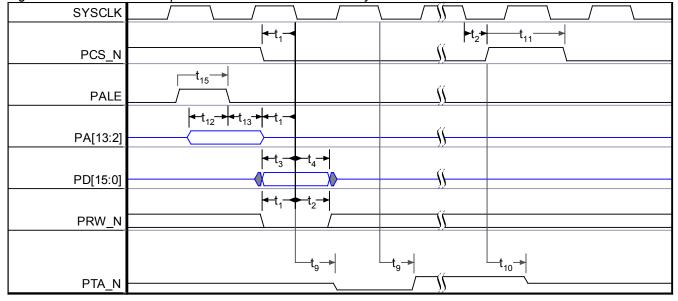

| Figure 13-4. MPC8313-like processor CPU Interface Read Cycle                                      |     |

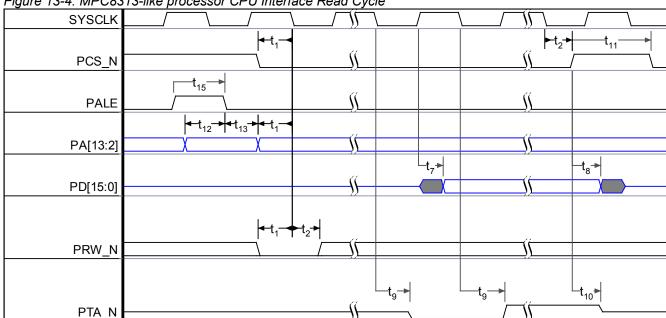

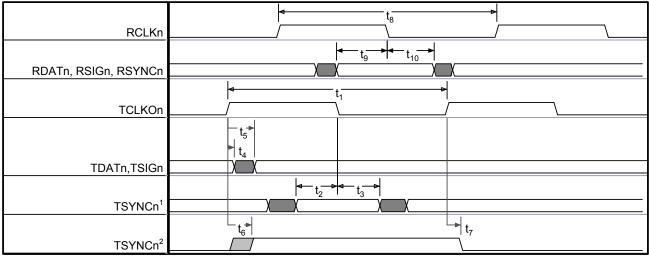

| Figure 13-5. TDM Port using Single Clock (TCLKO), positive edge timing (RSS = 1, TIES = RIES = 0) |     |

| Figure 13-6. TDM Port using Two Clock, negative edge timing (RSS = 0, TIES = RIES = 1)            |     |

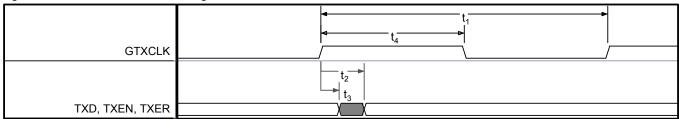

| Figure 13-7. GMII Transmit Timing                                                                 |     |

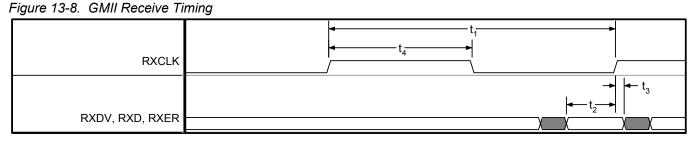

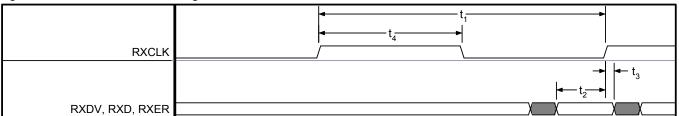

| Figure 13-8. GMII Receive Timing                                                                  |     |

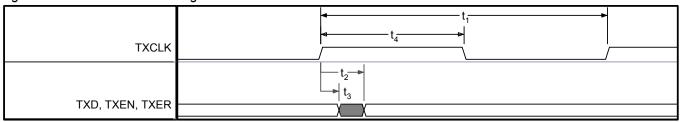

| Figure 13-9. MII Transmit Timing                                                                  |     |

| Figure 13-10. MII Receive Timing                                                                  |     |

| Figure 13-11. DDR SDRAM Timing                                                                    |     |

| Figure 15-1. 676-Ball TEPBGA (56-G6029-001)                                                       | 192 |

|                                                                                                   |     |

# **LIST OF TABLES**

|                                                                                          | 4.0                  |

|------------------------------------------------------------------------------------------|----------------------|

| Table 3-1. Applicable Standards                                                          |                      |

| Table 8-2. Detailed Pin Descriptions                                                     |                      |

| Table 9-2. TDM Port TCLKOn Clock Source Selection                                        |                      |

| Table 9-3. TDM Port BFD Settings                                                         |                      |

| Table 9-4. CAS Translation using RSIG and TSIG                                           |                      |

| Table 9-6. PDV Parameters that affect the latency of a PW packet                         | 42                   |

|                                                                                          |                      |

| Table 9-7. Maximum S132 Ethernet Media PDV                                               |                      |

| Table 9-8. Recognized PW Ethernet Types                                                  | 57                   |

| Table 9-9. Malformed PW Header Handling (not including the UDP specific settings)        |                      |

| Table 9-10. Bundle Forwarding Options                                                    | ອອ                   |

| Table 9-12. RXP CPU Header Descriptor – 1 <sup>st</sup> Dword                            |                      |

| Table 9-13. RXP CPU Header Descriptor – 2 <sup>nd</sup> Dword                            | 0 <del>4</del><br>65 |

| Table 9-14. RXP CPU Header Descriptor – 3 <sup>rd</sup> Dword                            | 65                   |

| Table 9-15. TXP CPU Header Control                                                       |                      |

| Table 9-16. Modify FCS and Add TXP OAM Timestamp Functions                               |                      |

| Table 9-17. SDRAM Device Selection Table                                                 |                      |

| Table 9-18. Interrupt Hierarchy                                                          |                      |

| Table 10-1. Register Block Address Ranges                                                |                      |

| Table 10-3. Global Configuration Registers                                               |                      |

| Table 10-4. Global Status Registers (G.)                                                 |                      |

| Table 10-5. Global Status Register Interrupt Enables (G.)                                |                      |

| Table 10-6. Bundle Reset Registers (G.)                                                  |                      |

| Table 10-7. Bundle Data Control Registers (B.)                                           |                      |

| Table 10-8. Bundle Data Registers (B.)                                                   |                      |

| Table 10-9. Bundle Status Latch Registers (B.)                                           |                      |

| Table 10-10. Bundle Status Register Interrupt Enables (B.)                               |                      |

| Table 10-11. Jitter Buffer Status Registers (JB.)                                        |                      |

| Table 10-12. Jitter Buffer Status Register Interrupt Enables (JB.)                       |                      |

| Table 10-13. Packet Classifier Configuration Registers (PC.)                             |                      |

| Table 10-14. Packet Classifier Register Latches (PC.)                                    | 113                  |

| Table 10-15. Packet Classifier Status Register Interrupt Enables (PC.)                   |                      |

| Table 10-16. Packet Classifier Counter Registers (PC.)                                   |                      |

| Table 10-17. External Memory Interface Configuration Registers (EMI.)                    |                      |

| Table 10-18. External Memory Interface Status Registers (EMI.)                           |                      |

| Table 10-19. External Memory Interface Status Register Interrupt Enables (EMI.)          |                      |

| Table 10-20. External Memory DLL/PLL Test Registers (EMI.)                               |                      |

| Table 10-21. Write Registers (EMA.)                                                      | 118                  |

| Table 10-22. Read Registers (EMA.)                                                       | 120                  |

| Table 10-23. Encap BERT Registers (EB.)                                                  |                      |

| Table 10-24. Decap BERT Registers (DB.)                                                  | 124                  |

| Table 10-25. Miscellaneous Diagnostic Registers (MD.)                                    |                      |

| Table 10-26. Test Registers (TST.)                                                       |                      |

| Table 10-27. MAC Registers (M.)                                                          | 129                  |

| Table 10-28. TXP SW CAS Registers (TXSCn.)                                               |                      |

| Table 10-29. Xmt (RXP) SW CAS Registers (RXSCn.)                                         |                      |

| Table 10-30. Port n Transmit Configuration Registers (Pn.)                               |                      |

| Table 10-31. Port n Transmit Status Registers (Pn.)                                      |                      |

| Table 10-32. Port n Transmit Status Register Latches (Pn.)                               | 143                  |

| Table 10-33. Port n Transmit Status Register Interrupt Enables (Pn.)                     | 143                  |

| Table 10-34. Port n Receive Configuration Registers (Pn.)                                |                      |

| Table 10-35. Port n Receive Status Registers (Pn.)                                       |                      |

| Table 10-36. Port n Receive Status Register Latches (Pn.)                                |                      |

| Table 10-37. Port n Receive Status Register Interrupt Enables (Pn.)                      |                      |

| Table 10-38. Timeslot Assignment Registers (TSAn.m.; "n" = TDM Port n; "m" = Timeslot m) |                      |

| Table 10-39. Global Ethernet MAC (M.) Control Register Settings (Values are in hex)      | 149                  |

| Table 10-40. Global Ethernet Packet Classification (PC.) Settings                                   |            |

|-----------------------------------------------------------------------------------------------------|------------|

| Table 10-41. Valid UDP BID Location and UDP Protocol Type Settings                                  | 151        |

| Table 10-42. Bundle and OAM Bundle Control Registers (B.)                                           | 151        |

| Table 10-43. SAT Bundle Settings                                                                    | 152        |

| Table 10-44. PMS/PDVT/MJBS for SAT with various PCT, PDV and BFD values                             | 152        |

| Table 10-45. CES without CAS Bundle Settings                                                        | 153        |

|                                                                                                     |            |

| Table 10-47. CES with CAS Bundle Settings                                                           | 154        |

| Table 10-48. PMS/PDVT/MJBS for T1/E1 CES with CAS for various PCT, PDV and BFD values               |            |

| Table 10-49. Unstructured HDLC Bundle (any Line Rate) Settings                                      |            |

| Table 10-50. Structured Nx64 Kb/s HDLC Bundle Settings                                              |            |

| Table 10-51. Structured 16 Kb/s or 56 Kb/s HDLC Bundle Settings                                     | 157        |

| Table 10-52. Combined RXP and TXP (Bidirectional) Clock Only Bundle Settings                        | 158        |

| Table 10-53. RXP (Unidirectional) Clock Only Bundle Settings                                        |            |

| Table 10-54. TXP (Unidirectional) Clock Only Bundle Settings                                        |            |

| Table 10-55. "CPU RXP PW Debug" Bundle Settings                                                     |            |

| Table 10-56. In-band VCCV OAM Connection Settings                                                   | 162        |

| Table 10-57. OAM Bundle PWID and Activation Control Registers (B.)                                  |            |

| Table 10-58. "Send to CPU" Quick Reference Settings                                                 |            |

| Table 10-59. Global TDM Port Settings                                                               |            |

| Table 10-60. TDM Port "n" Register Settings for T1 Applications (Pn.; n = 0 to 31)                  |            |

| Table 10-61. TDM Port "n" Register Settings for E1 Applications (Pn.; n = 0 to 31)                  |            |

| Table 10-62. TDM Port "n" Register Settings for non-T1/E1 Applications (Pn.; n = 0 to 31)           |            |

| Table 10-63. Ethernet MAC Status Registers (M.)                                                     |            |

| Table 10-64. Ethernet RMON Count Registers (M.; all are Read Only)                                  |            |

| Table 10-65. Global Packet Classifier Monitoring Settings (PC.)                                     | 168        |

| Table 10-66. Global RXP Bundle Control Word Change Monitor Settings(G.)                             | 168        |

| Table 10-67. Global TXP Output Queue Status Registers (G.)                                          |            |

| Table 10-68. TXP Bundle Status/Statistics Registers                                                 | 168        |

| Table 10-69. RXP Bundle Status/Statistics Registers <sup>3</sup>                                    |            |

| Table 10-70. SDRAM Settings (EMI.)                                                                  |            |

| Table 10-71. SDRAM Starting Address Assignments (EMI.; all SDRAM sizes)                             |            |

| Table 10-72. Example Max PDV (ms) for various PCT, JBMD and # of TS Combinations                    |            |

| Table 11-1. JTAG ID Code                                                                            |            |

| Table 12-1. Recommended DC Operating Conditions (T <sub>j</sub> = -40°C to +85°C.)                  |            |

| Table 12-2. DC Electrical Characteristics ( $T_j = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ .) | 1/3        |

| Table 13-1. CPU Interface Timing (VDD = 3.3V ±5%, Tj = -40°C to 125°C.)                             |            |

| Table 13-2. TDM Ports                                                                               |            |

| Table 13-3. GMII Transmit Timing                                                                    |            |

| Table 13-4. GMII Receive Timing                                                                     |            |

| Table 13-5. MII Transmit Timing                                                                     |            |

| Table 13-6. MII Receive Timing                                                                      |            |

| Table 13-7. DDR SDRAM Interface Timing                                                              |            |

| Table 14-1. Pins Sorted by Signal Name                                                              |            |

| Table 14-2. Pins Sorted by Ball Grid Array - Ball Number                                            |            |

| Table 14-3. Pin Assignments according to Device Outline                                             | 188<br>193 |

| ranie instrumental Parkane minimanon                                                                | 19.3       |

19-4750; Rev1; 7/11 **7 of 194**

### 1 INTRODUCTION

The public network is in transition from a TDM Switched Network to a Packet Switched Network. A number of Pseudowire (PW) packet protocols have been standardized to enable legacy TDM services (e.g. TDM voice, TDM Leased-line and HDLC encapsulated data) to be transported and switched/routed over a single, unified PSN. The legacy service is encapsulated into a PW protocol and then transported or tunneled through the unified PSN. The PW protocols provide the addressing mechanisms that enable a PSN to switch/route the service without understanding or directly regarding the specific characteristics of the services (e.g. the PSN does not have to directly understand the timing requirements of a TDM voice service). The PW protocols have been developed for use over PSNs that utilize the L2TPv3/IP, UDP/IP, MPLS (MFA-8) or Metro Ethernet (MEF-8) protocols.

PW protocols that are used for TDM services can be categorized as TDM-over-Packet (TDMoP) PW protocols. The TDMoP protocols support all of the aspects of the TDM services (data, timing, signaling and OAM). This enables Public (WAN) and Enterprise (LAN) networks to migrate to next generation PSNs and continue supporting legacy voice and leased-line services without replacing the legacy termination equipment.

Legacy TDM services depend on constant bit rate data streams with highly accurate frequency, jitter and wander timing requirements that up until recently have not been well supported by most packet switching equipment. For public network applications the timing recovery mechanisms must achieve the jitter and wander performance that is required by the ITU-T G.823/824/8261 standards. To accomplish this, a TDMoP terminating device must incorporate innovative and complex mechanisms to recovery the TDM timing from a stream of packets.

Legacy TDM services also have numerous special features that include voice signaling and OAM systems that have been developed over many years through a long list of standardization literature to provide carrier-grade reliability and maintainability. The list of legacy functions and features is so long that today's VoIP equipment only supports a subset of what is used in the legacy TDM network. This, in part, has slowed the transition from a TDM to Packet-based network. With TDMoP technology all features and services can be supported.

The TDMoP technology is similar to VoIP technology in that both provide a means of communicating a time oriented service (e.g. voice) over a non-time oriented, packet network. TDMoP technology can be added incrementally to the network (as needed) to supplement VoIP technology to provide an alternative solution when VoIP price/performance is not optimal (e.g. where the number of supported lines does not warrant the infrastructure required of a VoIP network) and where some function/features are not supported by the VoIP protocols.

The Legacy PSTN network also supports HDLC encapsulated data that is transported over TDM lines. PWs can also be used to transport HDLC data. This form of PW could also be categorized as a TDM service since the legacy service is carried over TDM lines. However, the fundamental aspects of an HDLC service do not depend as much on TDM timing and the nature of the data can be described as "packetized" as with Ethernet, Frame Relay and ATM services. For clarity the HDLC service is categorized as "HDLC over PW". One example Legacy HDLC service is SS7 Signaling which is used to communicate voice signaling information from one TDM switch to another.

19-4750; Rev1; 7/11 **8 of 194**

### 2 ACRONYMS AND GLOSSARY

- # Number

- ACR Adaptive Clock Recovery

- AT Absolute Timestamps

- ATM Asynchronous Transfer Mode

- BERT Bit Error Rate Test

- BGA Ball Grid Array

- BITS Building Integrated Timing System

- Bundle a PW with an ID that is recognized by the DS34S132

- BW Bandwidth

- CR Clock Recovery

- CAS Channel Associated Signaling

- CCS Common Channel Signaling

- CES abbreviation for CESoPSN

- CESoPSN Circuit Emulation Service over PSN

- CLAD Clock Rate Adapter

- CRE Clock Recovery Engine

- DA Destination Address

- DCR Differential Clock Recovery

- DCR-DT DCR with Differential Timestamps

- DDR Double Data Rate

- Decap –De-encapsulate

- DS0 64 Kb/s Timeslot within a T1 or E1 signal

- DS1 1.544 Mb/s TDM data stream

- E1 2.048 Mb/s TDM data stream

- Encap –Encapsulate

- EPON Ethernet PON (IEEE 802.3ah)

- FCS Frame Check Sequence

- GMII Gigabit MII (IEEE 802.3)

- GPON Gigabit PON (ITU-T G.984)

- GPS Global Positioning System

- HDLC High-level Data Link Control

- IEEE Institute of Electrical & Electronic Engineers

- IETF Internet Engineering Task Force

- IP Internet Protocol

- ISDN Integrated Services Digital Network

- ITU International Telecommunication Union

- JB Jitter Buffer

- L2TPv3 Layer 2 Tunneling Protocol Version 3

- LAN Local Area Network

- MAC Media Access Control

- MAN Metropolitan Area Network

- MEF Metro Ethernet Forum

- MFA MPLS/Frame Relay Alliance (Now called IP/MPLS Forum)

- MII Medium Independent Interface (IEEE 802.3)

- MPLS Multi-Protocol Label Switching

- OAM Operations, Administration & Maintenance

- OCXO Oven Controlled Crystal Oscillator

- OLT Optical Line Termination

- ONU Optical Network Unit

- PBX Private Branch Exchange

- PDV Packet Delay Variation

- PDVT PDV Tolerance

- PON Passive Optical Network

- PRBS Pseudo-Random Bit Sequence

- PSN Packet Switched Network

- PSTN Public Switched Telephone Network

- PWE3 Pseudo-Wire Edge-to-Edge Emulation

- PW Pseudo Wire

- QoS Quality of Service

- QRBS Quasi-Random Bit Sequence

- RAM Random Access Memory

- Rcv Receive

- RXP Receive Packet direction "from Ethernet Port to TDM Port"

- SAT abbreviation for SAToP

- SAToP Structure-Agnostic TDM over Packet

- SDH Synchronous Digital Hierarchy

- SDRAM Synchronous Dynamic RAM

- SN Sequence Number

- SONET –Synchronous Optical Network

- SS7 Signaling System 7

- T1 commonly used term for DS1

- T1-ESF T1 Extended Super-frame

- T1-SF T1 Super-frame

- T1/E1 T1 or E1

- TCXO Temperature Compensated Crystal Oscillator

- TDM Time Division Multiplexing

- TDMoIP TDM over IP

- TDMoP TDM over Packet

- Timeslot 64 Kb/s channel within an E1 or T1

- TS Timeslot

- TXP Transmit Packet direction "from TDM Port to Ethernet Port"

- UDP User Datagram Protocol

- VCCV Virtual Circuit Connectivity Verification

- VoIP Voice over IP

- WAN Wide Area Network

- Xmt Transmit

19-4750; Rev1; 7/11 9 of 194

# 3 APPLICABLE STANDARDS

Table 3-1. Applicable Standards

| Table 3-1. Applicable Standards SPECIFICATION TITLE |                                                                                                                            |  |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                     | G. 2511 107 (1101)                                                                                                         |  |  |

| ANSI<br>T1 100                                      | Digital Hierarchy Flectrical Interfaces 1003                                                                               |  |  |

| T1.102                                              | Digital Hierarchy—Electrical Interfaces, 1993                                                                              |  |  |

| T1.107                                              | Digital Hierarchy—Formats Specification, 1995                                                                              |  |  |

| T1.403                                              | Network and Customer Installation Interfaces—DS1 Electrical Interface, 1999                                                |  |  |

| ETSI                                                | 100N Discours Date Harry National Interface (UNIV) Date to Large 4 Once 1/4 0 0 (0000 05)                                  |  |  |

| ETS 300 011                                         | ISDN Primary Rate User Network Interface (UNI); Part 1: Layer 1 Spec. V1.2.2 (2000-05)                                     |  |  |

| IEEE                                                | N' (                                                                                                                       |  |  |

| IEEE 802.1Q                                         | Virtual Bridged Local Area Networks (2003)                                                                                 |  |  |

| IEEE 802.3                                          | Carrier Sense Multiple Access with Collision Detection Access Method and Physical Layer Spec. (2005)                       |  |  |

| IEEE 1149.1                                         | Standard Test Access Port and Boundary-Scan Architecture, 1990                                                             |  |  |

| IETF                                                |                                                                                                                            |  |  |

| RFC 4553                                            | Structure-Agnostic Time Division Multiplexing (TDM) over Packet (SAToP) (06/2006)                                          |  |  |

| RFC 4618                                            | Encapsulation Methods for Transport of PPP/High-Level Data Link Control (HDLC) over MPLS Networks (09/2006)                |  |  |

| RFC 5086                                            | Structure-Aware Time Division Multiplexed (TDM) Circuit Emulation Service over Packet Switched Network (CESoPSN) (12/2007) |  |  |

| RFC 5087                                            | Time Division Multiplexing over IP (TDMoIP) (12/2007)                                                                      |  |  |

| ITU-T                                               |                                                                                                                            |  |  |

| G.704                                               | Synchronous Frame Structures at 1544, 6312, 2048, 8448 and 44736 kbit/s Levels (10/1998)                                   |  |  |

| G.732                                               | Characteristics of Primary PCM Multiplex Equipment Operating at 2048Kbit/s (11/1988)                                       |  |  |

| G.736                                               | Characteristics of Synchronous Digital Multiplex Equipment Operating at 2048Kbit/s (03/1993)                               |  |  |

| G.823                                               | The Control of Jitter and Wander in Digital Networks Based on 2048kbps Hierarchy (03/2000)                                 |  |  |

| G.824                                               | The Control of Jitter and Wander in Digital Networks Based on 1544kbps Hierarchy (03/2000)                                 |  |  |

| G.8261/Y.1361                                       | Timing and Synchronization Aspects in Packet Networks (05/2006)                                                            |  |  |

| G.8261/Y.1361                                       | Timing and Synchronization Aspects in Packet Networks (12/2006). Corrigendum 1.                                            |  |  |

| 1.431                                               | Primary Rate User-Network Interface - Layer 1 Specification (03/1993)                                                      |  |  |

| O.151                                               | Error Performance Measuring Equipment Operating at the Primary Rate and Above (1992)                                       |  |  |

| Y.1413                                              | TDM-MPLS Network Interworking – User Plane Interworking (03/2004)                                                          |  |  |

| Y.1413                                              | TDM-MPLS Network Interworking – User Plane Interworking (10/2005). Corrigendum 1.                                          |  |  |

| Y.1414                                              | Voice Services–MPLS Network Interworking (07/2004)                                                                         |  |  |

| Y.1453                                              | TDM-IP Interworking – User Plane Networking (03/2006)                                                                      |  |  |

| MEF                                                 |                                                                                                                            |  |  |

| MEF 8                                               | Implementation Agree. for Emulation of PDH Circuits over Metro Ethernet Networks (10/2004)                                 |  |  |

| MFA                                                 |                                                                                                                            |  |  |

| MFA 8.0.0                                           | Emulation of TDM Circuits over MPLS Using Raw Encapsulation – Implement. Agree. (11/2004)                                  |  |  |

|                                                     | se sections of these standards that are affected by the DS34S132 functions are considered applicable. For                  |  |  |

Note: Only those sections of these standards that are affected by the DS34S132 functions are considered applicable. For example, several of the standards specify T1/E1 Framer/LIU functions (e.g. pulse shape) that are not included in the DS34S132 but also specify jitter/wander functions that are applicable.

19-4750; Rev1; 7/11 **10 of 194**

### 4 HIGH LEVEL DESCRIPTION

To implement a PW (tunnel) across a PSN requires a PW termination point at each end of the PW (tunnel). Each terminating point provides the PW encapsulation functions that are required to enter the PSN (for one direction of data) and the PW de-encapsulation functions to restore the data to its original (non-PW) format (for the opposite direction). The two data directions at each termination point can be can be described as the "transmit PW packet direction" (TXP) and the "receive PW packet direction" (RXP).

The DS34S132 TDMoP device implements the complete, bi-directional PW termination point encapsulation functions for TDMoP and HDLC PWs. The DS34S132 is a high density solution that can terminate up to 256 PWs that are associated with up to 32 T1/E1 data streams and aggregate that traffic for transmission over a single 100/1000 Mb/s Ethernet data stream. The DS34S132 can encap/decap TDMoP and HDLC PWs into the following PSN protocols: L2TPv3/IPv4, L2TPv3/IPv6, UDP/IPv4, UDP/IPv6, Metro Ethernet (MEF-8) and MPLS (MFA-8).

For TDMoP PWs the DS34S132 supports the SAToP and CESoPSN payload formats. SAToP is used for Unstructured TDM transport, where an entire T1/E1 including the framing pattern (if it exists) is transferred transparently as a series of unformatted bytes of data in the PW payload without regard to any bit, byte and/or frame alignment that may exist in the TDM data stream. The DS34S132 can support Unstructured T1, E1 or slower TDM data streams (any bit rate less than or equal to 2.048 Mb/s).

CESoPSN is used for Structured TDM transport where the PW packet payload is synchronized to the T1/E1 framing. With CESoPSN the T1/E1 framing pattern is commonly not passed across the PW (removed) because the structured PW format enables the framing information to be conveyed through the PW mechanisms. The opposite end generates the T1/E1 framing pattern from the PWs payload structure. This payload format can be used when the TDM service (e.g. voice) requires the ability to interpret, and/or terminate some functional aspects of the T1/E1 signal (e.g. identify DS0s within the T1/E1). PWs with the Structured payload format can support Nx64 Kb/s, fractional T1/E1 (T1: N = 1 - 24; E1: N = 1 - 32). In some applications, a T1/E1 can be divided into multiple Nx64 blocks (M x N x 64; M = the number of fractional blocks) and the PSN can be used as a "distributed cross-connect" to implement a point to multi-point topology forwarding some Nx64 blocks to one end point and other Nx64 blocks to other end points (T1: M = 1 - 24; E1: M = 1 - 32; e.g. for E1:  $32 \times 1 \times 64$ ).

The CESoPSN Structured format can also convey CAS Signaling across a PW through the use of a sub-channel within the CESoPSN PW packets. The DS34S132 enables the CAS Signaling to be transparently passed, monitored by an external CPU, and/or terminated by an external CPU, all on a per Timeslot and per direction basis.

The DS34S132 allows each TDM Port to independently support asynchronous or synchronous TDM data streams. Each TDM Port has a Clock Recovery Engine to regenerate the timing from a TDMoP PW packet data stream. For applications that do not require clock recovery the DS34S132 also provides several external clocking options.

The Clock Recovery Engines support Differential Clock Recovery (DCR) and Adaptive Clock Recovery (ACR). DCR can be used when a common clock is available at both ends of the PW (e.g. BITS clock for the public network or GPS for the mobile cellular network) and requires that the PW use RTP Timestamps to convey the TDM timing information. Adaptive Clock Recovery does not use Timestamps but instead regenerates the timing based on the TDMoP PW packet transmission rate. The DS34S132 high performance clock recovery circuits enable the use of PWs in the public network by achieving the stringent jitter and wander performance requirements of ITU-T G.823/824/8261, even for networks that impose large packet delay variation (PDV) and packet loss. For far end clock recovery, the DS34S132 can generate two Timestamp formats - Absolute and Differential Timestamps.

PWs can be used to transport HDLC packet data. The DS34S132 can forward HDLC encapsulated data transparently using a TDMoP PW (as described above; idle HDLC Flags are forwarded with the data) or by first extracting the data from the HDLC coding and then only forwarding the non-idle data in an HDLC PW. The HDLC PW is useful for HDLC data streams where a significant portion of the data stream is filled with HDLC Idle Flags. For example, if a 64 Kb/s TDM Timeslot is used to carry 4 Kb/s of HDLC data then it may be more bandwidth efficient to extract the payload data from the HDLC encoding and forward the data over an HDLC PW. The DS34S132 incorporates 256 HDLC Engines so that any PW can be assigned as a TDMoP PW or an HDLC PW.

PW Termination points often must also terminate OAM and Signaling packet data streams. To support this need the DS34S132 enables an external CPU to terminate several OAM and Signaling types including: PW In-band VCCV OAM, PW UDP-specific (Out-band VCCV) OAM, MEF OAM, Ethernet Broadcast frames, ARP, IPv6 NDP and includes a user specified CPU-destination Ethernet Type. The DS34S132 can also be programmed to forward packets to the CPU that match specialized conditions for debug or other purposes (e.g. wrong IP DA).

19-4750; Rev1; 7/11 11 of 194

The DS34S132 uses an external DDR SDRAM device to buffer data. The large memory supplies sufficient buffer space to support a 256 ms PDV for each of the 256 PW/Bundles and to enable packet re-ordering for packets that are received out of order (the PSN may mis-order the packets). This large memory is also used to buffer the HDLC data streams and the CPU terminated OAM and Signaling packets.

TDMoP provides the perfect transition technology for next generation packet networks enabling the continued use of the vast Legacy network and at the same time supplementing new packet based technologies.

19-4750; Rev1; 7/11 **12 of 194**

### 5 APPLICATION EXAMPLES

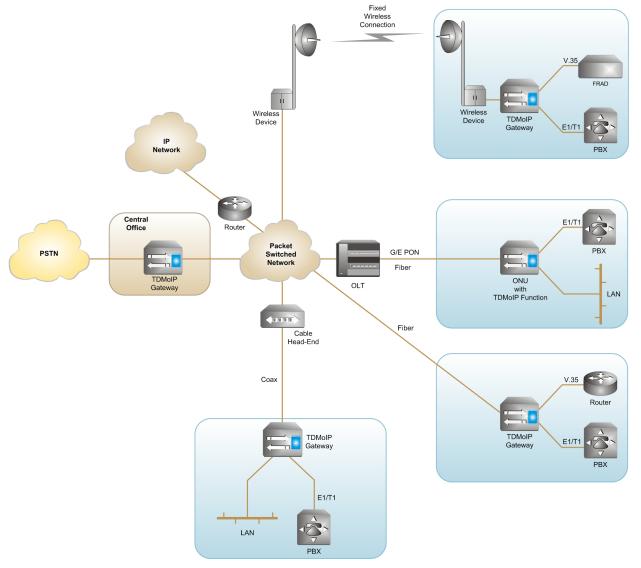

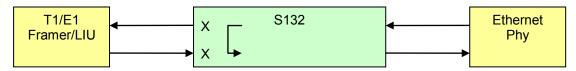

In Figure 5-1, TDMoP devices are used in gateway nodes to transport TDM services through a metropolitan PSN. The Maxim TDMoP family of devices offers a range of density solutions so that lower density solutions like the DS34T101 can be used in Service Provider Edge applications, to support a small number of T1/E1 lines, and higher density solutions like the DS34S132 can be used in Central Office applications, to terminate several Service Provider Edge nodes. PWs can be carried over fiber, wireless, SONET/SDH, G/EPON, coax, etc.

Figure 5-1. TDMoP in a Metropolitan Packet Switched Network

In Figure 5-2, DS34S132 devices are used in TDMoP gateways to enable TDM services to be transported through a Cellular Backhaul PSN.

19-4750; Rev1; 7/11 13 of 194

Figure 5-2. TDMoP in Cellular Backhaul

# **Other Possible Applications**

## **Using a Packet Backplane for Multiservice Concentrators**

Communications platforms with all/any of the above-mentioned capabilities can replace obsolete, low bandwidth TDM buses with low cost, high bandwidth Ethernet buses. The DS34S132 provides the interworking functions that are needed to packetize TDM services so that they can be multiplexed together with bursty services for transmission over a unified backplane bus. This enables a cost-effective, future-proof design with full support for both legacy and next-generation services.

19-4750; Rev1; 7/11 **14 of 194**

### 6 BLOCK DIAGRAM

Figure 6-1. DS34S132 Functional Block Diagram

19-4750; Rev1; 7/11 **15 of 194**

### 7 FEATURES

### **TDM Port Features**

- TDM Ports

- 32 TDM Ports, each with independently configured Framing Format

- T1/E1 Structured (with T1/E1 Framing)

- T1-SF, T1-ESF and E1 CAS Multi-frame formats

- With and Without CAS Signaling CAS embedded in data bus using RDAT/TDAT pins Parallel CAS Interface using RSIG/TSIG pins

- Unstructured (without Framing) T1, E1 and slower TDM line rates (any line rate ≤ 2.048 Mb/s)

### TDM Port Timing References

- TDM Port Clocks

- Asynchronous or Synchronous TDM Port Timing

- Independent Receive and Transmit Clocks

- Transmit TDM Port Timing

- RXP packet stream Clock Recovery

One Clock Recovery Engine per TDM Port

Global Clock Recovery Engine

- EXTCLK0 or EXTCLK1 External clock reference

- External RCLK signal (Loop timed)

- Receive TDM Port Timing

- External RCLK signal

- Internally generated Transmit timing (for synchronous systems)

- TDM Multi-frame Synchronization for CAS Signaling

- Independent Receive and Transmit Multi-frame Synchronization for each TDM Port

- E1, T1-SF and T1-ESF Multi-frame Synchronization

- External input or internally generated Multi-frame synchronization

### TDM Port Clock Recovery Engines

- Adaptive Clock Recovery or

- Differential Clock Recovery

- Common Clock (CMNCLK) frequency = 1MHz to 25MHz (in 8kHz increments)

- RTP Differential Timestamp

- Generation of Absolute Timestamps and Differential Timestamps

- External 5.0 MHz 155.52 MHz clock input (REFCLK) for internal Clock Recovery synthesizer

- Fast Frequency Acquisition and Highly Accurate Phase Tracking

- Recovered Clock Jitter and Wander per ITU-T G.823/G.824/G.8261 with Stratum 3 clock reference

- High resilience to Packet Loss and Robust to Sudden Significant Constant Delay Changes

- Automatic transition to hold-over during alarm/event impairments

### TDM Port Timeslot Assignment (TSA), CAS and Conditioning

- Nx64 Kb/s any combination of T1/E1 Timeslots from one TDM Port can be assigned to a PW/Bundle

- T1/E1 CAS Signaling (Channel Associated Signaling)

- Transparent CAS (forwarded from TDM to Ethernet Port and from Ethernet to TDM Port)

- Per Timeslot CPU Controlled CAS (CPU inserts CAS; in TXP and/or RXP directions)

- CAS Status and Change of Status for CPU Monitoring (in RXP and TXP directions)

- Data Conditioning can force any 8-bit pattern on any number of Timeslots (in RXP and TXP directions)

19-4750; Rev1; 7/11 **16 of 194**

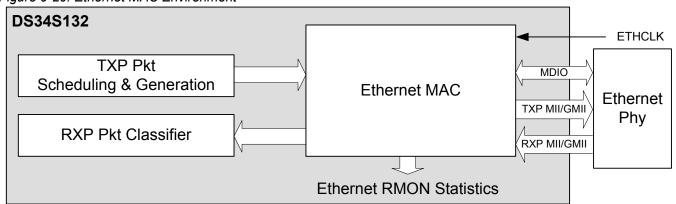

### **Ethernet Port Features**

- Ethernet MAC Interface

- 100/1000 Mb/s Operation using MII/GMII Interface

- 2 programmable receive Ethernet Destination Addresses

- Mixed Ethernet II (DIX) and IEEE 802.2 LLC/SNAP formats

- Mixed data streams with 0, 1, or 2 VLAN Tags

- Programmable VLAN TPID

- Ethernet Frame Length 64 bytes to 2000 bytes

#### **PW/Bundle Features**

- RXP PW/Bundle Header

- Up to 256 programmed PW/Bundles (32 per TDM Port)

- PW Header Types

- L2TPv3 / IPv6

- UDP / IPv4

- MEF (MEF-8)

- L2TPv3 / IPv4

- UDP / IPv6

- MPLS (MFA-8)

- Mixed MPLS data streams with 0, 1 or 2 MPLS Outer Labels

- Mixed L2TPv3 data streams with 0, 1, or 2 L2TPv3 Cookies

- Flexible UDP settings

- 16-bit (standard) or 32-bit (extended) UDP PW-ID bit width

- 16-bit UDP PW-ID selectable to be verified against UDP Source or Destination Port

- Optional 16-bit PW-ID Mask

- Ignore UDP Payload Protocol or verify against 2 programmable UDP Payload Protocol Values

- Optional PW Control Word

- Optional "In-band VCCV" Monitoring

- Programmable 16-bit In-band VCCV value with programmable 16-bit In-band VCCV mask

- Optional RTP Header

- One PW/Bundle per TDM Port can be assigned to provide RTP Timestamp for Clock Recovery

- Sequence Number

- Selectable between Control Word or RTP Sequence Number

- Used to initiate conditioning data when packets are missing

- Optional re-ordering of mis-ordered packets up to the Size of the Jitter Buffer depth

- Up to 32 UDP-Specific (Out-band VCCV) OAM PW-IDs

- Debug settings to forward PW/Bundles with special conditions to CPU for analysis (e.g. wrong IP DA)

- TXP PW/Bundle Header

- Store up to 256 CPU generated PW/Bundle Headers (one per PW/Bundle)

- Maximum 122 byte header with any CPU-specified content (Layer 2/3/4 content)

- Auto generate and insert Length and FCS functions for IP and UDP Headers

- Optional RTP Timestamp Insertion

- Any number of TXP PW/Bundles can be assigned to include Timestamp in RTP Header

- Optional RTP and Control Word Sequence Number Insertion

- 3 HDLC Sequence Number generation modes

- Sequence Numbers with "fixed at zero" value

- Sequence Numbers with incremented counting using "skip zero at Rollover"

- Sequence Numbers with incremented counting using "include zero at Rollover"

- PW/Bundle Payload Types

- TDMoP PW/Bundles (non-HDLC) Constant Bit Rate Services (e.g. PCM voice)

- Unstructured PW Payload (without framing; SAToP): E1, T1 and slower TDM bit rate (≤ 2.048 Mb/s)

- Structured PW Payload (with framing; CESoPSN)

- E1, T1-SF and T1-ESF formats

19-4750; Rev1; 7/11 **17 of 194**

- Any Nx64 Kb/s bit rate from a single T1 or E1 TDM Port

- With or without CAS Signaling

- HDLC PW/Bundles (e.g. SS7 Signaling)

- Unstructured PW Payload: E1, T1 and slower TDM bit rate (≤ 2.048 Mb/s)

- Structured PW Payload: Any Nx64 Kb/s bit rate from a single T1 or E1 TDM Port (for 8-bit HDLC)

### CES/SAT Processing

- 256 CES/SAT Engines (one per PW/Bundle)

- Per PW/Bundle Settings

- Any Payload Size (up to maximum 2000 byte Ethernet Packet length)

- Optional "zero" payload size for PW/Bundles that are only used for Clock Recovery

- RXP Jitter Buffer (to compensate for PDV and for packet re-ordering; up to 500 ms)

- Programmable "Begin Play-out Watermark" (for PDVT)

- TXP high or low priority queue scheduling

### HDLC Processing

- 256 HDLC Engines (one per PW/Bundle)

- Configurable Transmit TDM Port minimum number of Intra-frame Flags (1 to 8)

- Per Engine Settings

- 2-bit, 7-bit or 8-bit HDLC coding

- 16-bit, 32-bit or "no" Trailing HDLC FCS

- Intra-frame Flag Value (0xFF or 0x7E)

- HDLC Transmission Bit Order using MSB first or LSB first

#### **CPU Interface Features**

- CPU Packet Interface (for CPU-based OAM and Signaling)

- Stores up to 512 Transmit and 512 Receive Packets that can be 64 byte to 2000 byte in length

- RXP direction

- Provides detected packet type with each received RXP CPU packet

- In-band VCCV OAM

- UDP-specific (Out-band VCCV) OAM

- MEF OAM Ethernet Type

- Configured "CPU Ethernet Type"

- ARP

- Broadcast Ethernet DA

- Several Packet Header Conditions (e.g. NDP/IPv6 & unknown IP DA)

- Provides Local Timestamp indicating the time the packet was received (in 1 us or 100 us units)

- TXP direction

- Any CPU generated Header and Payload (any Layer 2/3/4 content)

- Support for IP FCS and UDP FCS Generation

- Optionally inserts TXP OAM Timestamps (in 1 us or 100 us units)

#### DS34S132 Control Interface

- MPC8xx or MPC83xx synchronous interface using a 50 to 80 MHz clock rate (the MPC8xx and MPC83xx are processor product families of Freescale Semiconductor, Inc.)

- Selectable 16-bit or 32-bit data bus

- DS34S132 device Control & Sense Registers

- Mask-able Interrupt Hierarchy for Change of Status, Alarms and Events

- Ethernet Port RMON Statistics

### **Miscellaneous**

- Loopbacks

- PW/Bundle Loopback (payload from RXP PW packets are transmitted in TXP PW packets)

- TDM Port Line Loopback (all data from Receive TDM Port sent to Transmit TDM Port using RCLK)

19-4750; Rev1; 7/11 **18 of 194**

- TDM Port Timeslot Loopback (from Receive to Transmit TDM Port Timeslot using RCLK)

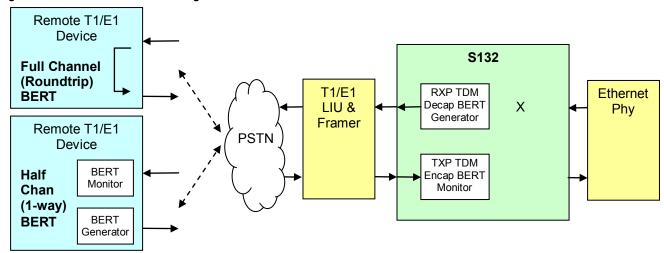

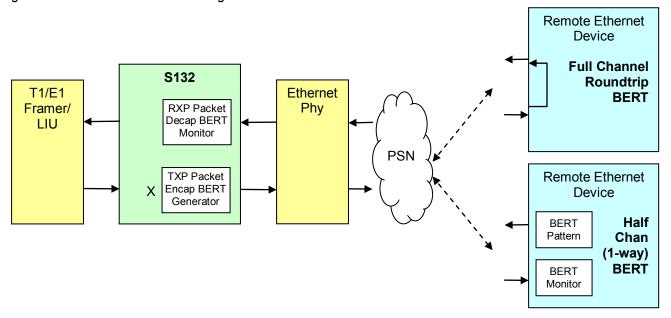

- TDM Port and/or Ethernet Port BERT Testing

- Half Channel (one-way) or Full Channel (round-trip) Testing

- Flexible PRBS, QRBS or Fixed Pattern Testing

- 16-bit DDR SDRAM Interface that does not require any glue-logic

- IEEE 1149.1 JTAG support

- MBIST (memory built-in self test)

- 1.8V Core, 2.5V DDR SDRAM and 3.3V I/O that are 5V tolerant

- 27 x 27 mm, 676-pin BGA package (1mm pitch)

19-4750; Rev1; 7/11 **19 of 194**

# **8 PIN DESCRIPTIONS**

# 8.1 Short Pin Descriptions

Table 8-1. DS34S132 Short Pin Descriptions

| Name               |                   | Function                                                                    |

|--------------------|-------------------|-----------------------------------------------------------------------------|

|                    | Type <sup>*</sup> |                                                                             |

| TDM Port n = 0 thr |                   |                                                                             |

|                    | Oz                | Transmit TDM Clock Output  Transmit Frame (Frame or Multi-frame Syme Bulge) |

| TSYNCn             | 10                | Transmit Frame (Frame or Multi-frame Sync Pulse)                            |

| TDAT <i>n</i>      | Oz                | Transmit NRZ Data                                                           |

| TSIGn              | Oz                | Transmit Signaling                                                          |

| RCLK <i>n</i>      | l<br>I            | Receive Clock Input                                                         |

| RSYNCn             | IO                | Receive Frame (Frame or Multi-frame Sync Pulse)                             |

| RDATn              | l                 | Receive NRZ Data                                                            |

| RSIGn              |                   | Receive Signaling                                                           |

| •                  |                   | C Interface (GMII/MII)                                                      |

| TXCLK              | lpu               | MII Transmit clock (25 MHz)                                                 |

| GTXCLK             | Oz                | GMII Transmit clock (125 MHz)                                               |

| TXD[7:0]           | Oz                | GMII/MII Transmit data                                                      |

| TXEN               | Oz                | GMII/MII Transmit data enable                                               |

| TXER               | Oz                | GMII/MII Transmit packet frame invalid                                      |

| RXCLK              | lpu               | GMII/MII Receive clock (25 MHz or 125 MHz)                                  |

| RXD[7:0]           | I                 | GMII/MII Receive data                                                       |

| RXDV               | I                 | GMII/MII Receive data valid                                                 |

| RXER               | I                 | GMII/MII Receive error                                                      |

| COL                | I                 | MII Collision Detection (not used)                                          |

| CRS                | ı                 | Carrier Sense Detection (not used)                                          |

| MDC                | Oz                | Management Data Clock                                                       |

| MDIO               | 10                | Management Data Input/Output                                                |

| CPU Interface      | L                 |                                                                             |

| PD[31:0]           | 10                | Data [31:0]                                                                 |

| PA[13:1]           | ı                 | Address [13:1]                                                              |

| PALE               | ı                 | Address Latch Enable                                                        |

| PCS N              | ı                 | Chip Select (active low)                                                    |

| PRW                | ı                 | Read/Write                                                                  |

| PRWCTRL            | I                 | Read/Write Control                                                          |

| PTA N              | Oz                | Transfer Acknowledge (active low)                                           |

| PWIDTH             | I                 | Processor Bus Width                                                         |

| PINT N             | Oz                | Interrupt Out (active low)                                                  |

| External Memory In |                   |                                                                             |

| SDCLK, SDCLK N     | Oz                | SDRAM Clock                                                                 |

| SDCLKEN            | Oz                | Clock Enable                                                                |

| SDCS N             | Oz                | Chip Select (active low)                                                    |

| SDRAS N            | Oz                | RAS (active low)                                                            |

| SDCAS N            | Oz                | CAS (active low)                                                            |

| SDWE N             | Oz                | Write Enable (active low)                                                   |

| SDBA[1:0]          | Oz                | Bank Address Select                                                         |

|                    |                   | Address  Address                                                            |

| SDA[13:0]          | Oz                | Bi-directional Data Bus                                                     |

| SDDQ[15:0]         | 10                |                                                                             |

| SDLDM              | Oz                | Lower Byte Data Mask                                                        |

| SDUDM              | Oz                | Upper Byte Data Mask                                                        |

19-4750; Rev1; 7/11 **20 of 194**

| SDLDQS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Name                | Type <sup>*</sup> | Function                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|------------------------------------------------------------------------|